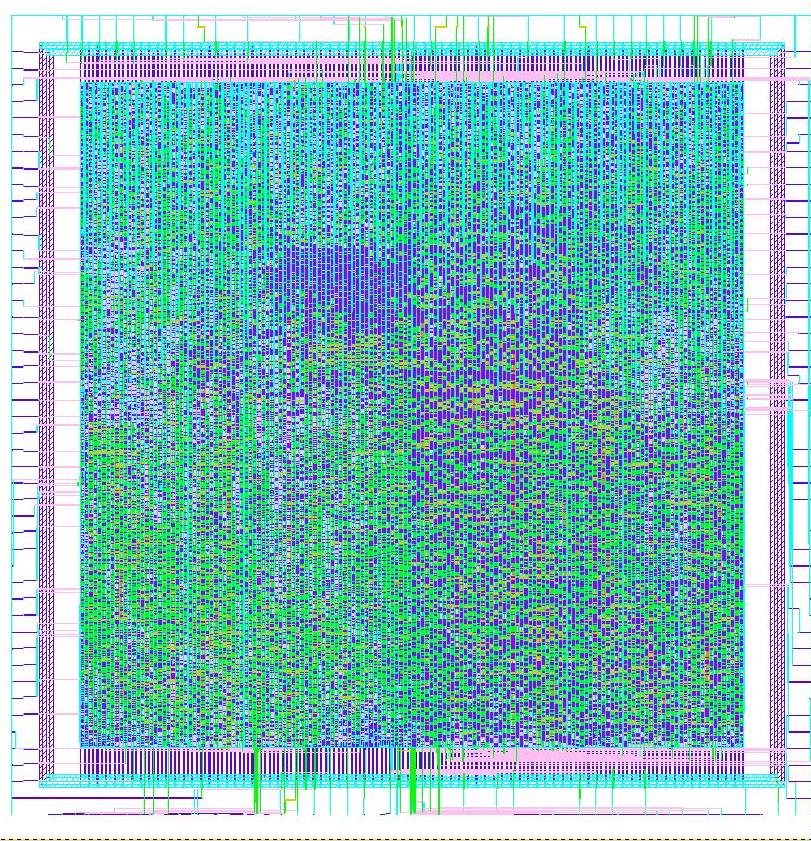

SAMIPS: A Synthesised Asynchronous MIPS Processor

SAMIPS is a Synthesised Asynchronous implementation of the MIPS R3000 processor core, supporting precise exceptions. SAMIPS was designed, modelled and automatically synthesised within the Balsa system. The development of SAMIPS took place at the University of Birmingham and was led by Professor Georgios Theodoropoulos as part of a collaborative research project with Professor Stephen Furber's APT Group in Manchester.

SAMIPS has been a pioneering effort:

- SAMIPS is one of the handful and one of the earliest asynchronous processors that have ever been developed.

- SAMIPS has been the first fully automatically synthesised asynchronous MIPS processor based on the theory of handshake circuits.

- Its design has developed novel algorithms for data hazards in asynchronous pipelines

- Its design has developed novel algorithms for addressing control hazards in asynchronous pipelines, including interrupts.

Software

- The Balsa source model of SAMIPS (BALSAMIPS) is here.

Publications

- Theodoropoulos, G., Zhang, Q., “A Distributed Colouring Scheme for Dealing with Control Hazards in Asynchronous Microprocessors”, The 7th International Symposium on Parallel Architectures, Algorithms, and Networks (I-SPAN 2004), May 10-12, 2004, Hong Kong. ISSN: 1087-4089, ISBN: 0-7695-2135-5. Pages 266-271. DOI Bookmark: 10.1109/ISPAN.2004.1300491

- Zhang, Q., Theodoropoulos, G., “Modelling SAMIPS: A Synthesisable Asynchronous MIPS Processor”, 37th Annual Simulation Symposium (IEEE/ACM/SCS), Part of the Advanced Simulation Technologies Conference (ASTC 2004), Hyatt Regency Crystal City Arlington, VA, April 18 - 22, 2004. ISSN: 1080-241X, ISBN:0-7695-2110-X, Pages: 205 – 212. DOI Bookmark: 10.1109/SIMSYM.2004.1299484

- Zhang, Q., Theodoropoulos, G., “Towards an Asynchronous MIPS Processor", The 8th Asia-Pacific Computer Systems Architecture Conference, (ACSAC'2003), Aizu-Wakamatsu City, Japan, September 23 - 26, 2003. Lecture Notes in Computer Science, Vol. 2823, ISBN 3-540-20122-X. Pages 137-150. DOI Bookmark: 10.1007/13479

- Zhang, Q., Theodoropoulos, G., "Towards an Asynchronous MIPS Processor", Presentation at the 3rd Working Group on Asynchronous Circuit Design Workshop (EC FP5 ACiD-WG), Heraklion, Crete, Greece, January 27-28, 2003.